# Projeto BIP: Impactos de 10 Anos de Uso de Uma Proposta Interdisciplinar de Ensino de Computação

Paulo Viniccius Vieira<sup>1</sup>, André Luis Alice Raabe<sup>1</sup>, Cesar Albenes Zeferino<sup>2</sup>

Laboratório de Inovação Tecnológica em Educação

Laboratório de Sistemas Embarcados e Distribuídos

Universidade do Vale do Itajaí

Itajaí, Brasil

paulovieira@univali.br, raabe@univali.br, zeferino@univali.br

Resumo —O Projeto BIP proporciona uma abordagem para o ensino de computação que se apoia no uso de um processador simples cujos conceitos são trabalhados e resgatados em várias disciplinas de Computação. O propósito inicial era reduzir o nível de abstração dos conceitos de programação introdutória a partir do entendimento de conceitos básicos de Arquitetura de abstra

partir do entendimento de conceitos básicos de Arquitetura de Computadores, no entanto as possibilidades de utilização do BIP transcenderam seu escopo inicial e envolveram diferentes disciplinas em que iniciativas foram implementadas com sucesso. Este artigo apresenta um relato dos resultados obtidos e do impacto do projeto iniciado no ano de 2006. Os resultados ilustram como o projeto possibilitou a integração dos conteúdos de diferentes disciplinas e como a temática fomentou a realização de projetos de extensão, projetos de iniciação científica, trabalhos de conclusão de cursos de graduação e de mestrado.

Palavras-chave — Ensino de Computação; Arquitetura de Computadores; Programação de Computadores.

#### I. INTRODUCÃO

A Arquitetura de Computadores é um dos pilares da formação em cursos de graduação em Computação, em especial os cursos de bacharelado em Ciência da Computação e em Engenharia de Computação. O domínio dos conceitos abordados em disciplinas dessa área é essencial para que o estudante compreenda aspectos sobre o funcionamento, o projeto e a programação dos computadores.

No primeiro ano de um curso de graduação, a compreensão dos aspectos básicos da arquitetura do computador fornece subsídios fundamentais para a aprendizagem e para a compreensão da lógica de programação. Entretanto, é fato conhecido que muitos alunos de fases iniciais apresentam dificuldades na aprendizagem de conceitos de algoritmos e programação [1]-[5]. Entre outros aspectos, essa dificuldade está relacionada à ausência de afinidade com o raciocínio lógico formal que é o fundamento para a capacidade de abstração dos alunos. Nesse sentido, o estudo da arquitetura do computador cria a possibilidade de estabelecer relações dos conceitos de programação com aspectos concretos do hardware, reduzindo assim a necessidade de abstração [6].

No entanto, alguns problemas podem ser identificados nos currículos de graduação, em especial nas fases iniciais dos cursos de bacharelado da área de Computação: (i) estudo da arquitetura e da organização do computador realizado apenas depois do ensino da programação; (ii) falta de uma articulação adequada entre professores das disciplinas de programação e de arquitetura, quando ministradas concorrentemente; e (iii) limitação dos modelos utilizados para a apresentação dos conceitos básicos de arquitetura.

Motivados pela busca por uma solução para esses problemas, pesquisadores da Universidade do Vale do Itajaí -Univali, iniciaram um projeto de pesquisa no ano de 2006 com o objetivo de auxiliar o aprendizado de conceitos de arquitetura de computadores com vistas a um melhor entendimento das abstrações utilizadas nas disciplinas da área de Algoritmos e Programação. Esse projeto foi centrado na especificação de uma arquitetura básica de processador com base em uma visão interdisciplinar dada pela participação de professores de disciplinas das áreas de Arquitetura de Processadores e de Programação. Sob essa visão, foi definida uma série de processadores com complexidade incremental para ilustrar conceitos básicos de arquitetura de computador a estudantes de disciplinas introdutórias de Programação. Além disso, a especificação considerou a possibilidade de uso dos processadores em disciplinas mais avançadas do curso. O processador proposto foi denominado BIP (Basic Instructionset Processor) e foi apresentado no 1º Workshop de Educação em Arquitetura de Computadores (WEAC) no ano de 2006.

A partir da especificação dos processadores BIP, foi desenvolvido um ambiente integrado para programação, além de diversos outros artefatos, os quais foram aplicados no ensino (e também em extensão). Com o amadurecimento do projeto diferentes disciplinas passaram a incluir o uso do processador BIP auxiliando a construir uma coesão curricular transversal. As atividades de desenvolvimento envolveram alunos de graduação e de pós-graduação em diversos projetos de pesquisa, com monografias, dissertações e artigos publicados.

Este artigo apresenta os resultados obtidos ao longo dos dez anos de execução do Projeto BIP e busca reportar e compartilhar a experiência adquirida nas atividades de ensino, pesquisa e extensão. As seções que seguem são organizadas da seguinte forma. A Seção II apresenta uma síntese da arquitetura do BIP, enquanto o ambiente de programação é descrito na Seção III. A Seção IV apresenta um relato do uso do BIP no ensino de graduação e de pós-graduação. A Seção V descreve os principais resultados obtidos nesses dez anos do projeto. Concluindo, a Seção VI apresenta as considerações finais.

# II. O PROCESSADOR BIP

A especificação do BIP foi baseada em diretrizes de projeto definidas para os processadores RISC (Reduced Instruction-Set Processor) [8] quanto à regularidade da arquitetura e à simplicidade da organização. No entanto, com o objetivo de definir uma arquitetura de menor complexidade que a dos processadores RISC tradicionais (e.g. MIPS, ARM), optou-se por adotar uma arquitetura orientada à acumulador, similar àquela utilizada nos microcontroladores PIC da Microchip [9].

Como citado anteriormente, foram especificados diversos modelos do processador BIP com complexidade incremental, desde o mais simples (BIP I) a um microcontrolador completo ( $\mu$ BIP – lê-se microBIP), com outros modelos intermediários (BIP II, III e IV). Todos os modelos são baseados nos atributos do modelo mais básico e estendem sua arquitetura com instruções e recursos adicionais. Os atributos arquiteturais do BIP I são:

- Palavras de dados e de instrução de 16 bits;

- Apenas um formato de representação de instruções;

- Espaços de endereçamento separados para instruções e dados:

- Entrada e saída mapeada na memória de dados; e

- Dois modos de endereçamento (imediato e direto).

A Tabela I apresenta as operações, quantidade de instruções e registradores do BIP I e o que foi adicionado nos demais modelos. O BIP I é essencialmente uma calculadora programável que suporta operações de soma e de subtração, além do acesso a variáveis em memória. O BIP II adiciona suporte para programação de estruturas de controle (desvios e laços de repetição), enquanto o BIP III acrescenta suporte para operações bit-a-bit. O BIP IV já acrescenta o suporte a procedimentos, entre outros. Por fim, o µBIP complementa os demais com o suporte necessário ao uso de periféricos. Detalhes adicionais sobre os conjuntos de instruções desses processadores podem ser encontrados em [6] e [10].

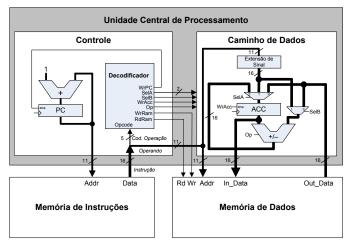

A Fig. 1 apresenta um diagrama de blocos que ilustra a organização do BIP I. O processador é divido no bloco de controle e no caminho de dados (bloco de processamento), sendo capaz de buscar, decodificar e executar uma instrução em um único ciclo de relógio (abordagem monociclo). Para isso, utiliza uma arquitetura Harvard, com memórias separadas para instruções e dados. Essa organização simplificada deriva da regularidade do conjunto de instruções e facilita em muito a implementação do processador, seja em modelos de simulação ou de síntese. Alternativamente, é possível adotar uma organização multiciclo com memórias unificadas (arquitetura de Von Neumann ou Princeton). Porém, isso acrescenta complexidade ao hardware.

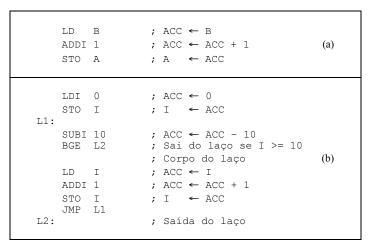

A Fig. 2 apresenta segmentos de código que ilustram o uso da linguagem de montagem do BIP. Primeiramente, é mostrado o código referente a um comando de atribuição com uma operação aritmética. Após, é mostrado o código equivalente a um comando de alto nível para um laço de repetição do tipo *for* escrito na linguagem de montagem do BIP II. Devido ao fato de utilizar um único formato para representar todas as instruções, não são suportadas instruções de comparação e desvio. Para isso, é necessário primeiramente executar uma subtração (*e.g.* SUBI 10) e depois uma instrução de desvio (*e.g.* BGE L2, ou seja, desvia para L2 se maior ou igual a 10).

Fig. 1. Organização do BIP I

Fig. 2. Exemplos de códigos na linguagem de montagem do BIP: (a) a = b + 1; e (b) for (i=0; i<10; i++) { }

# III. O AMBIENTE BIPIDE

Para apoiar o uso do BIP em disciplinas introdutórias de programação, foi desenvolvido um ambiente integrado com interface gráfica incluindo um editor de código fonte, compilador, montador e simuladores da arquitetura e da organização dos diferentes modelos do processador. Esse ambiente é denominado Bipide (de BIP IDE – Integrated Development Environment).

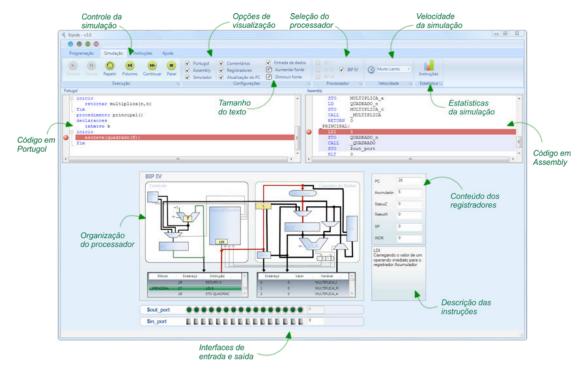

A interface do Bipide é ilustrada na Fig. 3, a qual mostra a aba de execução da simulação. Na figura, pode ser observado o código fonte em alto nível (escrito em Portugol), o seu equivalente na linguagem de montagem do BIP e a representação gráfica da organização sobre a qual são realizadas animações que mostram as movimentações de instruções e dados e as operações executadas.

TABELA I. ATRIBUTOS ARQUITETURAIS DOS PROCESSADORES BIP

| Modelo  | Operações suportadas                                                   | Instruções | Registradores adicionados  |

|---------|------------------------------------------------------------------------|------------|----------------------------|

| BIP I   | Operações aritméticas (+/- ) e acesso à memória                        | 8          | PC e ACC                   |

| BIP II  | Desvio condicional e incondicional                                     | 15         | STATUS                     |

| BIP III | Operações de lógica bit-a-bit                                          | 24         |                            |

| BIP IV  | Deslocamento lógico, chamada de procedimentos e manipulação de vetores | 28         | INDR e ToS                 |

| μBIP    | Interrupção por periféricos                                            | 29         | Específicos de periféricos |

onde: PC: Program Counter, ACC: Accumulator, INDR: Indirection Register, ToS: Top-of-Stack

Fig. 3. Interface do ambiente Bipide

A primeira versão do Bipide [11] incluiu um compilador para a linguagem de alto nível Portugol, a qual é utilizada como primeira linguagem na disciplina Algoritmos e Programação do curso de bacharelado em Ciência da Computação da Univali. Após, na versão 4.0 [12], foi incluído um compilador para linguagem C.

Dentre as diferentes características do Bipide que auxiliam o aprendizado, pode-se ressaltar: (i) destaque simultâneo do comando em alto nível em execução e das instruções correspondentes na linguagem de montagem; (ii) animação da busca da instrução e da execução das operações; (iv) controle da velocidade da simulação; (iii) descrição textual da instrução em execução; e (v) estatísticas das instruções executadas.

#### IV. USO DO BIP NO ENSINO

O BIP tem sido utilizado no ensino em cursos de graduação e de pós-graduação da área de Computação da Univali desde 2006, em especial no curso de bacharelado em Ciência da Computação.

# A. Uso no curso de bacharelado em Ciência da Computação

Na disciplina Algoritmos e Programação (1º período, 120 horas), o BIP I é utilizado para reduzir a abstração e ilustrar a representação em hardware de conceitos de programação, tais como: variável, constante, atribuição, operação aritmética, comandos com múltiplas operações, desempenho dos programas e papel do compilador. Após aprenderem a programação em alto nível na linguagem Portugol, os alunos aprendem como cada comando de alto nível é escrito com o uso de instruções da linguagem de montagem do BIP e, então, simulam a execução dos seus programas no Bipide. Após, o BIP II é utilizado para ilustrar a implementação e a execução de estruturas de controle no programa. As dificuldades dos estudantes em compreender conceitos abstratos foram significativamente reduzidas, conforme foi constatado em uma avaliação empírica com um design quase-experimental [11].

Na disciplina Computação Básica (1º período, 60 horas), o BIP é usado como processador de referência para ilustrar os

conceitos básicos de arquitetura e de organização de computadores. Por meio da análise de uma versão simplificada da organização ilustrada na Fig. 1, é mostrado como são realizadas as operações de busca e de execução das suas diferentes instruções.

Na disciplina Circuitos Digitais (2º período, 60 horas), o BIP é usado como estudo de caso para integração de conceitos abordados quanto ao projeto de componentes do processador (e.g. registradores, somador/subtrator, decodificador, multiplexador). A disciplina é baseada em ferramentas de captura de esquemático e os blocos desenhados pelos alunos são interligados para formar o processador.

Na disciplina Arquitetura e Organização de Computadores I (3º período, 60 horas), o BIP é utilizado como primeiro exemplo de processador para ilustrar os conceitos de arquitetura e de organização. A partir dele, é feito então o estudo do processador MIPS e ambos são comparados quanto às suas características arquiteturais.

Na disciplina Compiladores (8º período, 60 horas), o BIP é usado como alternativa para demonstrar todas as fases de construção do compilador seguindo a abordagem sugerida em [13], na qual inicia-se definindo a arquitetura da linguagem alvo para então se definir os aspectos sintáticos e léxicos da linguagem de alto nível. A ferramenta Bipide tem sido utilizada como ambiente para simular a execução do *assembly* gerado pelos compiladores desenvolvidos pelos estudantes. A abordagem tem auxiliado a ilustrar detalhadamente o processo de transformação de linguagem de alto nível em linguagem de montagem e o efeito de sua execução na modificação dos estados do hardware. Foi observada também uma melhoria significativa no desempenho dos estudantes com uso do binômio BIP-Bipide, a qual foi reportada em [23].

O uso do BIP nessas quatro disciplinas seguindo essa abordagem multi- e interdisciplinar proporcionou uma série de beneficios aos estudantes. Em primeiro lugar, foi possível alcançar uma integração mais natural entre os conceitos de programação, circuitos digitais, arquitetura de computadores e compiladores tratados nas disciplinas. Seguindo, observou-se

uma redução de problemas de aprendizagem relacionados com as abstrações envolvidas nos conceitos introdutórios de programação, tais como: variáveis, constantes e atribuições. Também se verificou uma maior facilidade na consolidação de conceitos de arquitetura e organização de computadores pelo uso de uma arquitetura de referência em diferentes disciplinas. Na disciplina Compiladores, em particular, ao utilizar o conjunto de instruções do BIP, a etapa de geração de código dos trabalhos de compiladores foi concluída pela maioria dos alunos. Um relato mais detalhado do uso do BIP nessas disciplinas é apresentado em [6].

# B. Uso em outros cursos na área de Computação

O BIP também tem sido utilizado como processador de referência para apoiar o ensino de linguagem de descrição de hardware na disciplina Projeto de Sistemas Digitais (60 horas) do 8º período do curso de Engenharia de Computação e em disciplina de mesmo nome no Mestrado em Computação Aplicada. A simplicidade da arquitetura e da organização do BIP aceleram o entendimento da especificação do processador pelos alunos e permitem focar as atividades no entendimento de como uma linguagem de descrição de hardware (no caso, VHDL) é usada para implementar um processador.

#### C. Uso no Programa CI Brasil

O processador BIP tem sido utilizado no Programa Nacional de Formação de Projetista de Circuitos Integrados [24], uma das ações do Programa CI Brasil do Ministério de Ciência, Tecnologia e Inovação. Esse programa tem por objetivo ampliar a formação de projetistas de CIs de nível internacional no País através de treinamento profissional, por meio de cursos ministrados em seus Centros de Treinamento.

Para uso no Programa, a arquitetura do BIP foi estendida de modo cobrir uma faixa maior de conceitos. Essa versão foi denominada Charrua e tem sido adotada como estudo de caso na Fase 1 do treinamento desde 2012, com 183 alunos treinados. Conforme reportado pelos responsáveis pelos Centros de Treinamento do Programa CI Brasil, a regularidade da arquitetura permitiu reduzir o tempo para aprendizado dos conceitos abordados no curso de formação.

# V. RESULTADOS DO PROJETO

Ao longo dos seus dez anos de execução, o projeto BIP envolveu a execução de diferentes projetos com a participação de estudantes de graduação e de mestrado nas atividades referentes ao desenvolvimento dos artefatos de hardware e de software.

#### A. Monografias e dissertações

Com relação às monografias de graduação, em [14], foi realizada a especificação, implementação e prototipação em FPGA (Field-Programmable Gate Array) do µBIP. Em [15], periféricos foram integrados de comunicação microcontrolador. Em [16], foi implementado o suporte para configuração da memória do processador para carga do programa em FPGA. A primeira versão do Bipide foi desenvolvida em [17] e atualizada em [18] com a inclusão do suporte a vetores e a chamadas de sub-rotinas (versão 3.0). Em [19] (versão 4.0), foi introduzido o suporte à linguagem C. Em [20], foi realizada a integração do Bipide com outro compilador didático a fim de unificar as sintaxes utilizadas. Em [21], foi desenvolvido um sistema operacional de tempo real para o µBIP. Destaca-se que o trabalho [17] foi agraciado com o prêmio de melhor monografia de graduação em concurso promovido pela Sociedade Brasileira de Computação no Simpósio Brasileiro de Informática na Educação - SBIE no ano de 2009.

Em nível de mestrado, em [23] foi realizado um estudo para avaliar o impacto do uso do BIP e do Bipide no ensino. Esse trabalho, foi premiado com Menção Honrosa no Concurso de Teses e Dissertações do Congresso Brasileiro de Informática na Educação no ano de 2013.

#### B. Projetos executados

De 2008 a 2010, foi executado um projeto focado na avaliação empírica do uso do BIP no ensino de programação, o qual contou com apoio do CNPq (Edital Universal) e da Capes (Programa Prosup), trabalho esse conduzido no escopo da dissertação de mestrado [23], já citada.

De 2012 a 2013, com o apoio do CNPq, por meio da Chamada CNPq/VALE No. 05/2012 – Forma Engenharia, foi realizado um projeto de extensão com um grupo de quatro estudantes do Colégio de Aplicação da Univali. Nesse projeto, alunos do 1º e do 2º ano do ensino médio foram capacitados na programação e na implementação de processadores utilizando o BIP, conforme relatado em [22]. Como resultado principal, destaca-se que os quatro alunos formados no projeto ingressaram em cursos de bacharelado em Engenharia de Computação e de Ciência da Computação, atendendo aos objetivos do programa Forma-Engenharia.

Uma segunda edição do projeto de extensão supracitado foi realizada de 2014 a 2015 e contou com o apoio do CNPq por meio Chamada Pública MCTI/CNPq/SPM-PR/Petrobras No. 18/2013, a qual tinha como foco a atração de alunas (meninas) para cursos de Ciências Exatas, Engenharias e Computação. Participaram do projeto quatro estudantes de ensino médio do Colégio de Aplicação da Univali. As alunas desenvolveram habilidades para construir aplicações com uso de linguagem de programação e compreenderam noções fundamentais de eletrônica e desenvolvimento de processadores. A bolsista que atuou como monitora do projeto (aluna de graduação em engenharia de computação) desenvolveu com sucesso habilidades de docência e passou a atuar nos projetos subsequentes ligados ao tema.

Como desdobramento desses dois projetos, a partir de 2015, com fomento do programa de extensão da Univali, foi iniciado um terceiro projeto de extensão em parceria com a escola pública Nereu Ramos de Itajaí que participa do Programa de Ensino Médio Inovador — ProEMI [25] do Ministério da Educação. O projeto tem como foco desenvolver o pensamento computacional em uma perspectiva *maker*, ou seja, proporciona aos estudantes aprender conceitos de computação a partir de atividades práticas que envolvem a criação de artefatos físicos. Da mesma forma que em projetos anteriores, o uso do BIP tem auxiliado a reduzir a abstração necessária para compreender o funcionamento do computador e alguns dos componentes de sua organização têm sido construídos pelos estudantes em *protoboards*.

# C. Publicações

Em decorrência dos projetos, monografias e dissertações realizadas nesses dez anos, o Projeto BIP propiciou a disseminação dos produtos e conhecimentos produzidos por meio de diversas publicações, cujos indicadores estão sumarizados na Tabela II.

TABELA II. PUBLICAÇÕES PRODUZIDAS NO PROJETO

| Tipo de publicação        | Quantidade |  |

|---------------------------|------------|--|

| Capítulo de livro         | 1          |  |

| Artigo em periódico       | 5          |  |

| Artigo em anais de evento | 12         |  |

| Monografia de graduação   | 8          |  |

| Dissertação de mestrado   | 1          |  |

Os principais veículos de divulgação científica utilizados foram periódicos e anais de eventos na área de Educação em Computação publicados pela SBC, tais como: RBIE (Revista Brasileira de Informática na Educação), IJCAE (International Journal on Computer Architecture Education), WEAC (Workshop de Educação em Arquitetura de Computadores), WIE (Workshop de Informática na Escola) e SBIE (Simpósio Brasileiro de Informática na Educação). Trabalhos de natureza tecnológica foram também divulgados em eventos das áreas de Sistemas de Computação e de Microeletrônica, incluindo: IP-SoC (IP-Based Electronic System Conference & Exhibition), SBESC (Simpósio Brasileiro de Engenharia de Sistemas Computacionais), SPL (Southern Programmable Logic Conference), SIM (South Symposium on Microelectronics), SForum (Microelectronics Students Forum). Esse elenco de veículos ilustra a amplitude de oportunidades para divulgação de resultados de projetos similares ao Projeto BIP.

# D. Cooperação interdisciplinar

Umas das dificuldades observadas em instituições de ensino e pesquisa é a promoção da cooperação entre grupos de pesquisa de diferentes áreas ou de subáreas de uma mesma área. Nesse sentido, o Projeto BIP serviu de ponte para estabelecer uma relação duradoura entre dois laboratórios cujos focos de pesquisa não apresentavam um enlace anterior. O problema identificado quanto à necessidade de melhorar o aprendizado dos alunos em uma disciplina de programação e a proposta de uma solução que pudesse ser aproveitada em outras disciplinas estabeleceu a referida ponte.

Em especial, quando grupos com enfoques bem diferentes como Informática na Educação e Sistemas de Computação passam a trabalhar em conjunto, os desafios e as possibilidades de crescimento são igualmente ampliadas. Aprender a considerar diferentes enfoques, equilibrar demandas pedagógicas com demandas técnicas, formar alunos e pesquisadores com fluência técnica e também com fundamentos pedagógicos, conciliar diferentes estilos de realizar pesquisa e de produzir resultados, são desafios que foram e são abordados continuamente e possibilitam a ampliação da qualidade, abrangência e relevância do que vem sendo pesquisado e construído.

Além disso, os professores que lecionam disciplinas com potencial para utilizar conceitos do BIP encontram apoio de uma equipe sólida, com *know-how* historicamente construído para apoiá-los, além de oportunidades para se integrarem em atividades de pesquisa nos temas relacionados.

#### VI. CONCLUSÕES

A elaboração deste artigo proporcionou aos envolvidos uma reflexão sobre os aspectos do projeto que tiveram maior impacto e que tem auxiliado na formação de estudantes da área de computação. Esse exercício é salutar uma vez que permite reconhecer o que tem tido bons resultados e o que poderia ou necessitaria ser revisado. Nesse sentido, sintetiza-se a seguir o

que destacamos como principais benefícios dos dez anos de trabalho com o projeto BIP:

#### A. Melhorias no processo de ensino aprendizagem

A análise realizada em [26] confirma que os esforços dispendidos para a evolução da família de processadores BIP e do ambiente Bipide aumentaram seu potencial pedagógico, permitindo desde o desenvolvimento e simulação de algoritmos simples até programas mais complexos. Essa amplitude de possibilidades favoreceu a adoção do BIP como modelo de processador em diferentes disciplinas do curso de graduação em Ciência da Computação da Univali

O estudo realizado em [11] verificou que a utilização do BIP e do Bipide na disciplina Algoritmos e Programação reduziu a abstração dos conceitos vistos na disciplina e propiciou uma melhoria de desempenho dos alunos na ordem de 1,93 pontos na média, com 99% de confiança.

As avaliações realizadas em [23] demonstraram que a inclusão dos processadores BIP na disciplina Compiladores produziu um efeito de melhoria na média dos alunos. Esses alunos também perceberam melhor a influência da arquitetura do computador nas diferentes etapas de construção de um compilador. Essas descobertas são fortalecidas pelos resultados obtidos no grupo focal conduzido em [27], no qual os alunos expressaram que a simplicidade da arquitetura e do conjunto de instruções do BIP colaborou para a realização das atividades e trabalhos realizados durante a disciplina.

# B. Melhoria na interdisciplinaridade do currículo

O BIP proporciona uma conexão natural entre conteúdos de diferentes disciplinas, pois possui a simplicidade necessária para isso. Outros modelos de processador dificilmente permitem essa abordagem. Com isso, os estudantes percebem a relação entre os conceitos relacionados nas disciplinas envolvidas de forma facilitada e com base em um exemplo concreto. Essas melhorias são também evidenciadas nos resultados qualitativos coletados em [23].

# C. Integração, Ensino, Pesquisa e extensão

Como ilustram os resultados detalhados na Secão V deste artigo, a concepção, implantação, verificação, aprimoramento, experimentação e consolidação do BIP e Bipide foram realizados por meio de diversos trabalhos de cunho científico e tecnológico. Os resultados dessas pesquisas geraram um produto educacional que tem beneficiado os estudantes da universidade e de escolas da região e por meio de projetos de extensão. Mais do que apenas ter ações nas três esferas, as demandas de ensino apresentadas por estudantes e professores se transformam em problemas de pesquisa que foram abordados em projetos de diferentes níveis. Os estudantes que utilizam os artefatos conceituais e ferramentas em suas disciplinas de graduação, são os mesmos que têm oportunidades para ampliá-las, modificá-las ou estendê-las a partir de ideias que muitas vezes são próprias. O envolvimento de estudantes de menor idade, nos projetos de extensão, tem possibilitado refletir sobre modelos concretos que podem auxiliar na compreensão de componentes da organização de um processador.

As perspectivas de continuidade do projeto buscam ampliar o escopo de utilização das ferramentas desenvolvidas, coletar evidencias de outras instituições que têm utilizado o BIP e ampliar e organizar o material desenvolvido para facilitar a adoção da proposta em outras instituições.

#### AGRADECIMENTOS

O Projeto BIP e seus subprojetos contaram com apoio de programas de apoio à pesquisa e à extensão do CNPq, da Capes e da Univali.

#### REFERÊNCIAS

- [1] A. Carbone e J. Kaasboll, "A survey of methods used to evaluate computer science teaching," In *Proc. of the 3rd Conference on Teaching of Computing*, 1998, p. 41-45.

- [2] B. Haberman e O. Muller, "Teaching abstraction to novice pattern-based and ADT-based problems-solving processes", In: Proc. of 38th Annual Frontiers in Education Conference, 2008, p. F1C-7 - F1C-12.

- [3] E. P. Pimentel, V. F. Franca, R. V. Noronha e N. Omar, "Avaliação contínua da aprendizagem, das competências e habilidades em programação de computadores," In Anais do XXIII Congresso da Sociedade Brasileira de Computação Workshop de Informática na Escola, 2003.

- [4] V. G. Renumol, D. Janafiram e S Jayaprakash, "Identification of Cognitive Processes of Effective and Ineffective Students During Computer Programming," ACM Transactions on Computing Education, v. 10, n. 3, p. 0,0, 2010.

- [5] J. T. Khalife, "Threshold for the introduction of Programming: Providing Learners with a Simple Computer Model," In *Proc. of the 28th Int. Conf. on Information Technology Interfaces*, 2006, p. 71-76.

- [6] C. A. Zeferino, A. A. Raabe, P. V. Vieira e M. C. Pereira, "Um Enfoque Interdisciplinar no Ensino de Arquitetura de Computadores," In C. A. P. S. Martins, P. O. A. Navaux, R. J. Azevedo, S. T. Kofuji (Org.), Arquitetura de Computadores: educação, ensino e aprendizado. 1ed. Porto Alegre: Sociedade Brasileira de Computação (SBC), 2012, p. 165-193

- [7] D. Morandi, A. L. A. Raabe e C. A. Zeferino, "Processadores para Ensino de Conceitos Básicos de Arquitetura de Computadores," In: Proc. of 18th Int. Symp. on Computer Architecture and High Performance Computing – Workshop de Educação em Arquitetura de Computadores, 2006. p. 17-24.

- [8] D. A. Patterson e J. L. Hennessy, Organização e projeto de computadores: a interface hardware/software, 4.ed., 2014.

- [9] Microchip, PIC16F62X Data Sheet: FLASH-Based 8-Bit CMOS Microcontroller, 2003.

- [10] P. V. Vieira, P. R. M. Rech, R. Mensch, C. A. Zeferino e A. L. A. Raabe, "Estendendo a Arquitetura dos Processadores BIP para Ampliar o Seu Potencial de Uso em Disciplinas de Introdução a Programação," *International Journal of Computer Architecture Education* (IJCAE), v. 1, 2012.

- [11] P. V. Vieira, A. L. A. Raabe e C. A. Zeferino, "Bipide: ambiente de desenvolvimento integrado para a arquitetura dos processadores BIP," *Revista Brasileira de Informática na Educação*, v. 18, p. 32-43, 2010.

- [12] N. P. de Oliveira Junior, A. L. A. Raabe e C. A. Zeferino, "Implementando Suporte a Novas Linguagens de Programação e outros Idiomas no Ambiente de Desenvolvimento Integrado Bipide,"

- International Journal of Computer Architecture Education, v. 3, p. 5-8, 2014.

- [13] R. D. Lins, "Uma Proposta de Plano Pedagógico para a matéria de Compiladores," In Anais do Congresso da Sociedade Brasileira de Computação - II Curso de Qualidade de Cursos de Graduação da Área de Computação e Informática, Congresso Anual da SBC, 2000.

- [14] M. C. Pereira, "BIP: Microcontrolador Básico para o Ensino de Sistemas Embarcados," Trabalho de Conclusão de Curso (Graduação em Ciência da Computação), Universidade do Vale do Itajaí, 2008.

- [15] D. F. M. Santiago, "uBIP: Adição de Protocolos de Comunicação em Microcontrolador Básico," Trabalho de Conclusão de Curso. (Graduação em Ciência da Computação), Universidade do Vale do Itajaí, 2009.

- [16] A. Vulczak, "Modelo sintetizável do uBIP com interface para configuração da memória de programa," Trabalho de Conclusão de Curso (Graduação em Ciência da Computação), 2015

- [17] P. V. Vieira, "Bipide: Ambiente de Desenvolvimento Integrado para Utilização dos Processadores BIP no Ensino de Programação," Trabalho de Conclusão de Curso (Graduação em Ciência da Computação), Universidade do Vale do Itajaí, 2009.

- [18] P. R. M. Rech, "BIP IV: Especificação e Suporte na IDE Bipide," Trabalho de Conclusão de Curso (Graduação em Ciência da Computação), Universidade do Vale do Itajaí, 2011.

- [19] N. P. de Oliveira Junior, "Criação de um compilador da linguagem C para a arquitetura dos processadores BIP,". Trabalho de Conclusão de Curso. (Graduação em Ciência da Computação), Universidade do Vale do Itajaí, 2013.

- [20] P. Mannes, "Integração do Portugol Core com o Bipide," Trabalho de Conclusão de Curso. (Graduação em Ciência da Computação), Universidade do Vale do Itajaí, 2013.

- [21] H. W. M. S. Gonçalves, "Análise e portabilidade de um sistema operacional de tempo real para o uBip," Trabalho de Conclusão de Curso (Graduação em Ciência da Computação), Universidade do Vale do Itajaí, 2013.

- [22] F. Viel, A. L. A. Raabe e C. A. Zeferino, "Introdução à programação e à implementação de processadores por estudantes do Ensino Médio," In Anais do 30 Congresso Brasileiro de Informática na Educação Workshop de Informática na Escola, 2014. p. 1-10.

- [23] P. V. Vieira, "Avaliação empírica da proposta interdisciplinar de uso dos processadores BIP," Dissertação (Mestrado em Computação Aplicada), Universidade do Vale do Itajaí, 2013.

- [24] CI Brasil, Programa Nacional de Formação de Projetistas de Circuitos Integrados, Disponível em: <a href="http://www.ci-brasil.gov.br/index.php/pt/programa-de-formacao">http://www.ci-brasil.gov.br/index.php/pt/programa-de-formacao</a>

- [25] MEC, Ensino Médio Inovador, Disponível em: http://portal.mec.gov.br/component/content/article?id=13439:ensino-medio-inovador

- [26] P. V. Vieira, C. A. Zeferino e A. L. A. Raabe, "Avaliação empírica da proposta interdisciplinar de uso dos processadores BIP", Revista Brasileira de Informática na Educação, v. 23, n. 2, p. 99-110, 2015.

- [27] P. V. Vieira, C. A. Zeferino e A. L. A. Raabe, "Aplicação de grupo focal para avaliação da utilização de uma familia de processadores simplificados em uma disciplina de compiladores" In *Anais do Computer on the Beach*, 2016, p. 232-241.